## Simulink<sup>®</sup> Design Verifier<sup>™</sup> User's Guide

# MATLAB® & SIMULINK®

## How to Contact MathWorks

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

T

Phone: 508-647-7000

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

Simulink® Design Verifier™ User's Guide

© COPYRIGHT 2007–2017 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

Prover, Prover Technology, Prover Plug-In and the Prover logo are trademarks or registered trademarks of Prover Technology AB in Sweden, the United States and in other countries. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### **Patents**

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

## **Revision History**

| May 2007       | Online only | New for Version 1.0 (Release 2007a+)    |

|----------------|-------------|-----------------------------------------|

| September 2007 | Online only | Revised for Version 1.1 (Release 2007b) |

| March 2008     | Online only | Revised for Version 1.2 (Release 2008a) |

| October 2008   | Online only | Revised for Version 1.3 (Release 2008b) |

| March 2009     | Online only | Revised for Version 1.4 (Release 2009a) |

| September 2009 | Online only | Revised for Version 1.5 (Release 2009b) |

| March 2010     | Online only | Revised for Version 1.6 (Release 2010a) |

| September 2010 | Online only | Revised for Version 1.7 (Release 2010b) |

| April 2011     | Online only | Revised for Version 2.0 (Release 2011a) |

| September 2011 | Online only | Revised for Version 2.1 (Release 2011b) |

| March 2012     | Online only | Revised for Version 2.2 (Release 2012a) |

| September 2012 | Online only | Revised for Version 2.3 (Release 2012b) |

| March 2013     | Online only | Revised for Version 2.4 (Release 2013a) |

| September 2013 | Online only | Revised for Version 2.5 (Release 2013b) |

| March 2014     | Online only | Revised for Version 2.6 (Release 2014a) |

| October 2014   | Online only | Revised for Version 2.7 (Release 2014b) |

| March 2015     | Online only | Revised for Version 2.8 (Release 2015a) |

| September 2015 | Online only | Revised for Version 3.0 (Release 2015b) |

| October 2015   | Online only | Rereleased for Version 2.8.1 (Release   |

| 3.5 1 004.0    | 0.11        | 2015aSP1)                               |

| March 2016     | Online only | Revised for Version 3.1 (Release 2016a) |

| September 2016 | Online only | Revised for Version 3.2 (Release 2016b) |

| March 2017     | Online only | Revised for Version 3.3 (Release 2017a) |

| September 2017 | Online only | Revised for Version 3.4 (Release 2017b) |

## Contents

## Acknowledgments

| Key Features  Simulink Design Verifier Block Library  Analyze a Model  About This Example  Open the Model  Generate Test Cases  Combine Test Cases  Generate Test Cases for a Subsystem  Analyze a Stateflow Atomic Subchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Simulink Design Verifier Block Library  Analyze a Model  About This Example  Open the Model  Generate Test Cases  Combine Test Cases  Generate Test Cases for a Subsystem  Analyze a Stateflow Atomic Subchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| Analyze a Model  About This Example Open the Model Generate Test Cases Combine Test Cases  Generate Test Cases for a Subsystem  Analyze a Stateflow Atomic Subchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

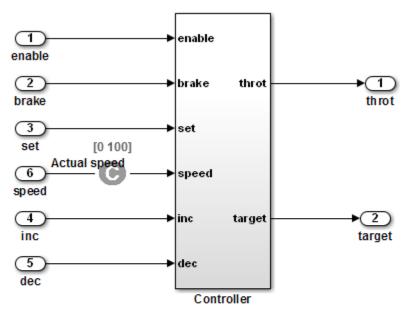

| About This Example Open the Model Generate Test Cases Combine Test Cases  Generate Test Cases for a Subsystem  Analyze a Stateflow Atomic Subchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . <b>.</b> |

| Open the Model Generate Test Cases Combine Test Cases  Generate Test Cases for a Subsystem  Analyze a Stateflow Atomic Subchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| Generate Test Cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |

| Simulink Design Verifier Product Description Key Features  Simulink Design Verifier Block Library  Analyze a Model About This Example Open the Model Generate Test Cases Combine Test Cases 1  Generate Test Cases for a Subsystem 1  Analyze a Stateflow Atomic Subchart Analyze an Atomic Subchart Using the Simulink Design Verifier Software 1  Basic Workflow for Simulink Design Verifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| Simulink Design Verifier Block Library  Analyze a Model About This Example Open the Model Generate Test Cases Combine Test Cases Combine Test Cases 1  Generate Test Cases for a Subsystem 1  Analyze a Stateflow Atomic Subchart Analyze an Atomic Subchart Using the Simulink Design Verifier Software 1  Basic Workflow for Simulink Design Verifier 1  How the Simulink Design Verifier Software Workflow the Simulink Design Verifier Software Workflow for Simulink Design Verifier Software Workflow the Simulink Design Verifier Software Workflow for |            |

| Analyze a Stateflow Atomic Subchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 1        |

| v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 1        |

| Analyze an Atomic Subchart Using the Simulink Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1          |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 1        |

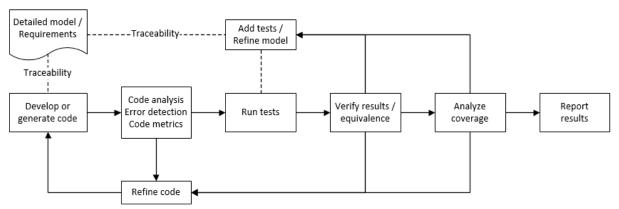

| Basic Workflow for Simulink Design Verifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 1        |

| How the Simulink Design Verifier Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Wor        |

| Inlined Parameters  Large Models  Handle Incompatibilities with Automatic Stubbing What Is Automatic Stubbing? How Automatic Stubbing Works Analyze a Model Using Automatic Stubbing  Nonfinite Data  Approximations Approximations Types of Approximations Floating-Point to Rational Number Conversion Linearization of Two-Dimensional Lookup Tables for Floating- | 2-7<br>2-8<br>2-8<br>2-8 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Large Models  Handle Incompatibilities with Automatic Stubbing What Is Automatic Stubbing? How Automatic Stubbing Works Analyze a Model Using Automatic Stubbing  Nonfinite Data  Approximations Approximations During Model Analysis Types of Approximations Floating-Point to Rational Number Conversion                                                            | 2-8                      |

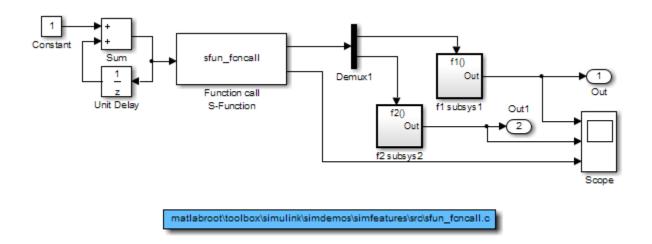

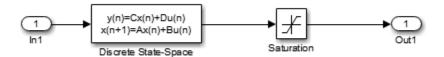

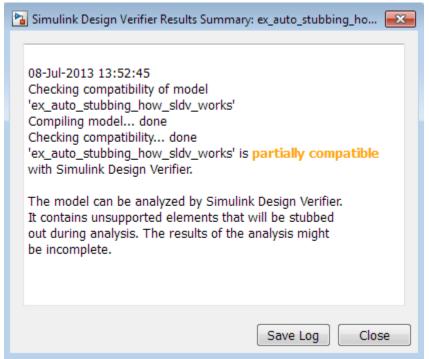

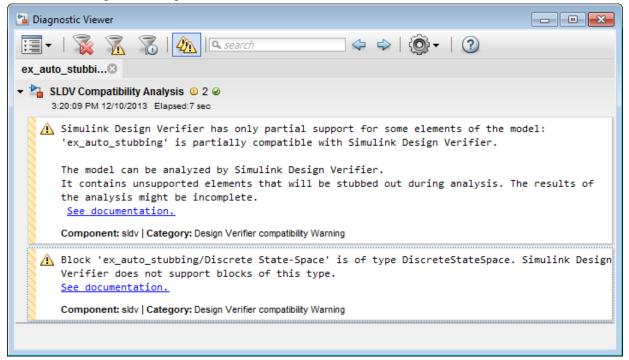

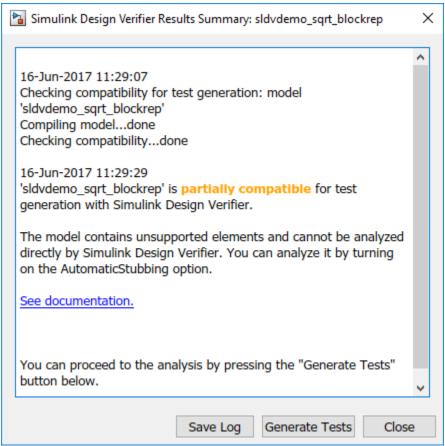

| Handle Incompatibilities with Automatic Stubbing  What Is Automatic Stubbing?  How Automatic Stubbing Works  Analyze a Model Using Automatic Stubbing  Nonfinite Data  Approximations  Approximations  Types of Approximations  Floating-Point to Rational Number Conversion                                                                                          | 2-8<br>2-8<br>2-8        |

| What Is Automatic Stubbing? How Automatic Stubbing Works Analyze a Model Using Automatic Stubbing  Nonfinite Data  Approximations Approximations During Model Analysis Types of Approximations Floating-Point to Rational Number Conversion                                                                                                                           | 2-8<br>2-8               |

| How Automatic Stubbing Works Analyze a Model Using Automatic Stubbing  Nonfinite Data  Approximations Approximations During Model Analysis Types of Approximations Floating-Point to Rational Number Conversion                                                                                                                                                       |                          |

| Analyze a Model Using Automatic Stubbing                                                                                                                                                                                                                                                                                                                              | 2-8<br>2-10              |

| Nonfinite Data  Approximations  Approximations During Model Analysis  Types of Approximations  Floating-Point to Rational Number Conversion                                                                                                                                                                                                                           | 2-10                     |

| Approximations                                                                                                                                                                                                                                                                                                                                                        |                          |

| Approximations During Model Analysis                                                                                                                                                                                                                                                                                                                                  | 2-14                     |

| Types of Approximations                                                                                                                                                                                                                                                                                                                                               | 2-15                     |

| Floating-Point to Rational Number Conversion                                                                                                                                                                                                                                                                                                                          | 2-15                     |

|                                                                                                                                                                                                                                                                                                                                                                       | 2-15                     |

|                                                                                                                                                                                                                                                                                                                                                                       | 2-16                     |

| Point Data Types                                                                                                                                                                                                                                                                                                                                                      | 2-16                     |

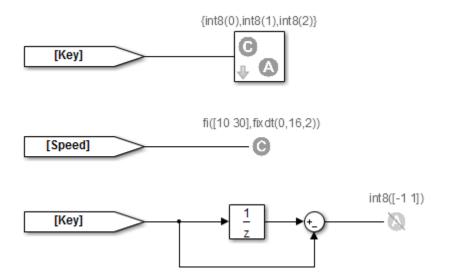

| Integer and Fixed-Point Data Types                                                                                                                                                                                                                                                                                                                                    | 2-17                     |

| While Loops                                                                                                                                                                                                                                                                                                                                                           | 2-17                     |

| Reporting Approximations Through Validation Results                                                                                                                                                                                                                                                                                                                   | 2-19                     |

| Impact of Approximations on Objectives Status Identifying the Effect of Approximations Through Validation                                                                                                                                                                                                                                                             | 2-19                     |

| Results                                                                                                                                                                                                                                                                                                                                                               | 2-20                     |

| Logic Operations Short-Circuiting                                                                                                                                                                                                                                                                                                                                     | 2-23                     |

| Checking Compatibility with the Simulink Des<br>Verifier Softw                                                                                                                                                                                                                                                                                                        | _                        |

|                                                                                                                                                                                                                                                                                                                                                                       |                          |

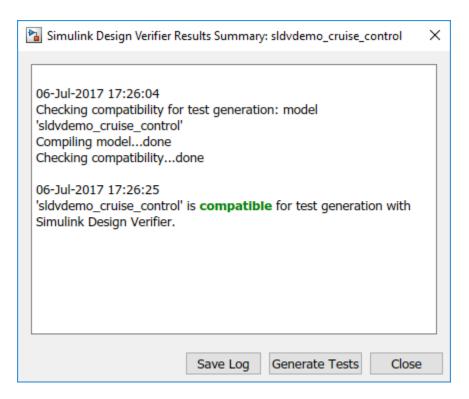

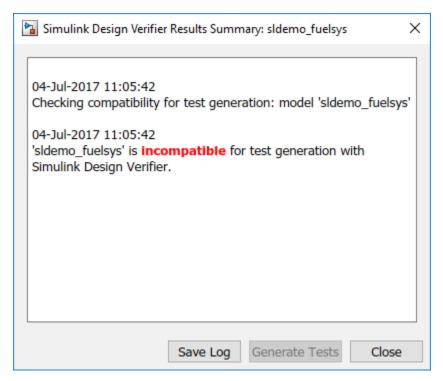

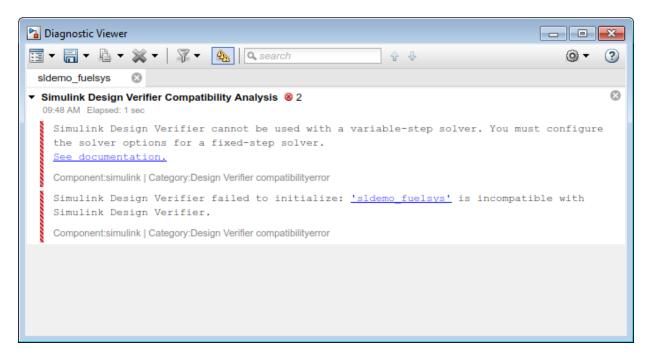

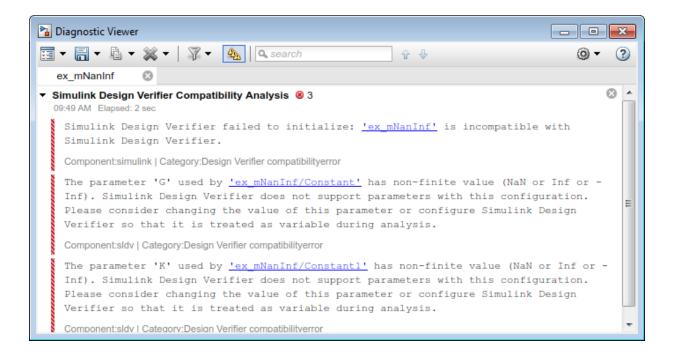

| Check Model Compatibility                                                                                                                                                                                                                                                                                                                                             | 3-2                      |

| Compatibility with Simulink Design Verifier                                                                                                                                                                                                                                                                                                                           | 3-2                      |

| Run Compatibility Check                                                                                                                                                                                                                                                                                                                                               | 3-2                      |

| Compatibility Check Results                                                                                                                                                                                                                                                                                                                                           | 3-3                      |

| Supported and Unsupported Simulink Blocks in Simulink Design Verifier                                                                                                                                | 3-10                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Support Limitations for Simulink Software Features                                                                                                                                                   | 3-22                                         |

| Support Limitations for Model Blocks                                                                                                                                                                 | 3-25                                         |

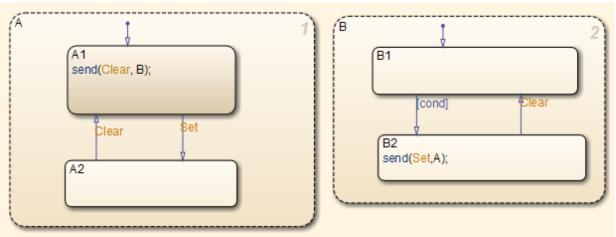

| Support Limitations for Stateflow Software Features ml Namespace Operator, ml Function, ml Expressions C Math Functions                                                                              | 3-27<br>3-27<br>3-27                         |

| Outside a Subchart  Atomic Subchart Input and Output Mapping  Recursion and Cyclic Behavior  Custom C or C++ Code  Machine-Parented Data  Textual Functions with Literal String Arguments            | 3-28<br>3-28<br>3-28<br>3-30<br>3-30<br>3-31 |

| Support Limitations for MATLAB for Code Generation Unsupported MATLAB for Code Generation Features Support Limitations for MATLAB for Code Generation Library Functions                              | 3-32<br>3-32<br>3-32                         |

| Support Limitations for S-Functions  Enabling S-Functions in Simulink Design Verifier  Support Limitations for S-Function Code  Considerations for Enabling S-Functions in Simulink Design  Verifier | 3-37<br>3-37<br>3-38                         |

| Source code protection                                                                                                                                                                               | 3-38                                         |

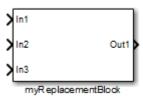

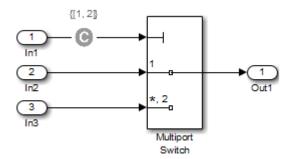

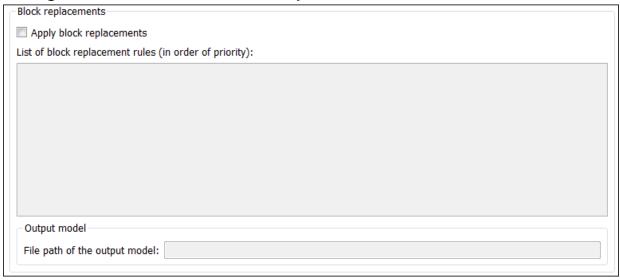

| What Is Block Replacement?                                                                                                                                                                           | 4-2<br>4-3                                   |

| Built-In Block Replacements                                                                                                                                                                          | 4-6                                          |

| Template for Block Replacement Rules                                                                                                                                                                 | 4-8                                          |

|                                                                                                                                                                                                      |                                              |

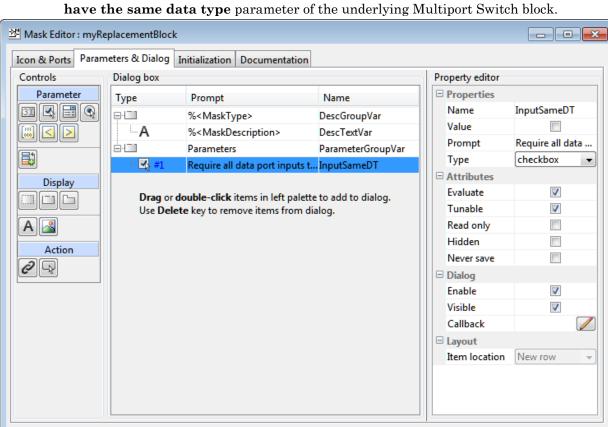

| Define Custom Block Replacements                       | 4-9                                                       |

|--------------------------------------------------------|-----------------------------------------------------------|

| Basic Workflow for Defining Custom Block Replacements  | 4-9                                                       |

| Specify Replacement Blocks                             | 4-9                                                       |

| Write Block Replacement Rules                          | 4-10                                                      |

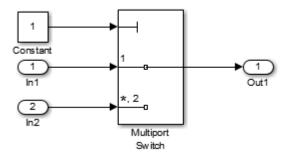

| Replace Multiport Switch Blocks                        | 4-10                                                      |

| Execute Block Replacements                             | 4-17                                                      |

| Configure Block Replacements                           | 4-17                                                      |

| Replace Blocks in a Model                              | 4-18                                                      |

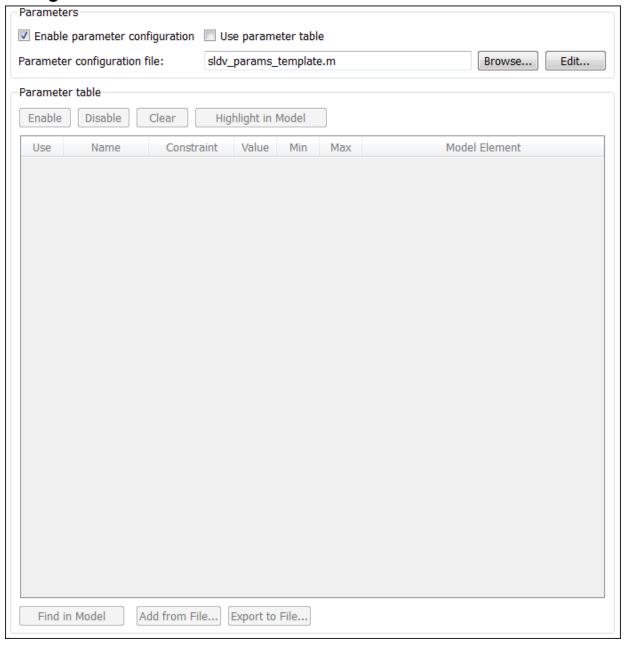

| Specifying Parameter Configuration                     | ions                                                      |

|                                                        |                                                           |

| Parameter Constraint Values                            | 5-2                                                       |

| Parameter Configuration for Analysis                   | 5-2                                                       |

| Data Types in Parameter Configurations                 | <b>5</b> -3                                               |

| Parameters in Variant Subsystems                       | 5-4                                                       |

| Define Constraint Values for Parameters                | 5-5                                                       |

| Find Parameters and Autogenerate Constraints           | 5-7                                                       |

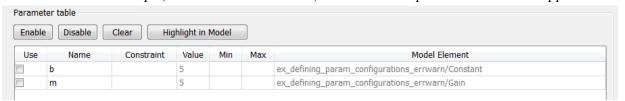

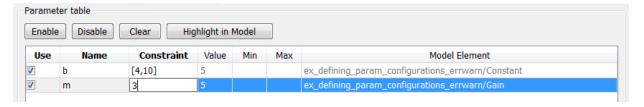

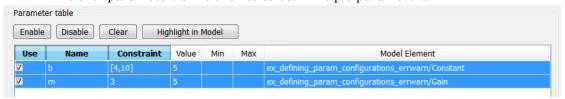

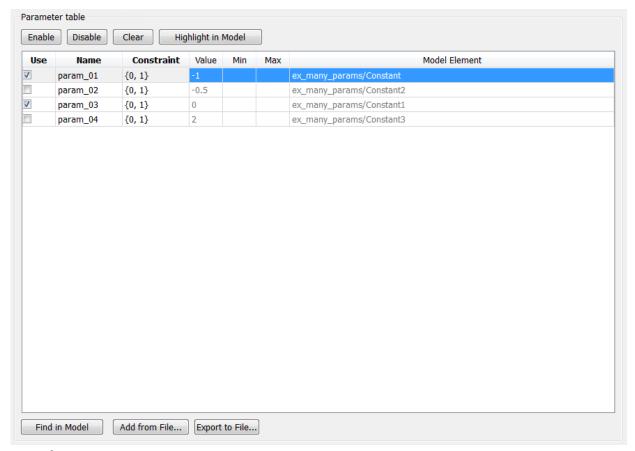

| Edit Parameter Constraints                             | 5-9                                                       |

| Highlight Constrained Parameters in Model              | 5-10                                                      |

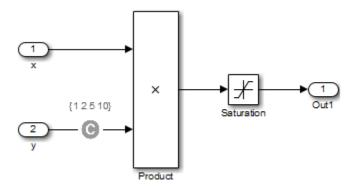

| Specify Parameter Constraint Values for Full Coverage  | 5-12                                                      |

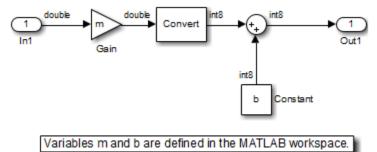

| About This Example                                     | 5-12                                                      |

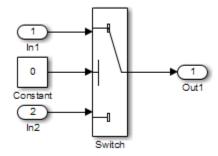

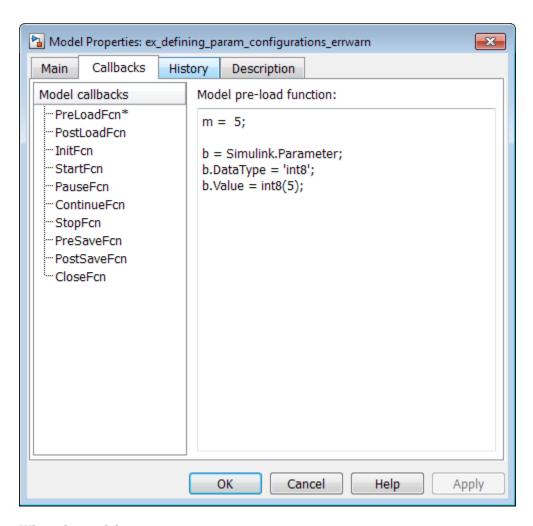

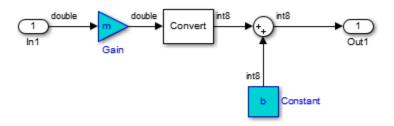

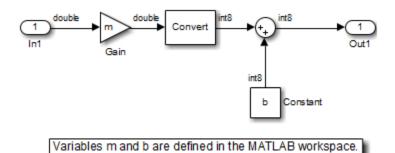

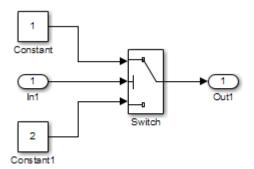

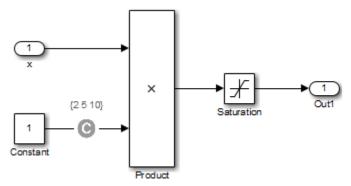

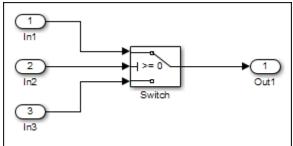

| Construct Example Model                                | 5-13                                                      |

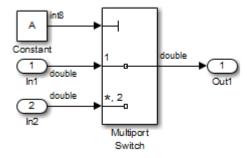

| Parameterize Constant Block                            | 5-14                                                      |

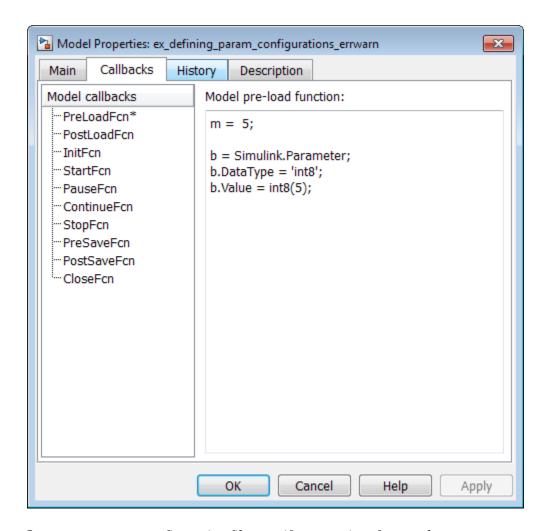

| Preload Workspace Variable                             | 5-14                                                      |

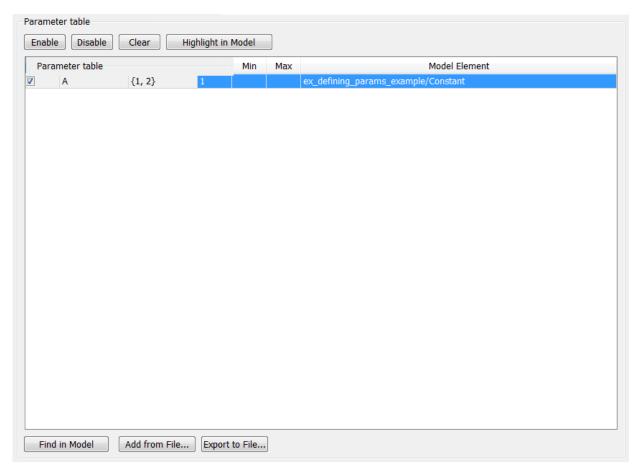

| Autogenerate Parameter Constraint                      | 5-15                                                      |

| Analyze Example Model                                  | 5-17                                                      |

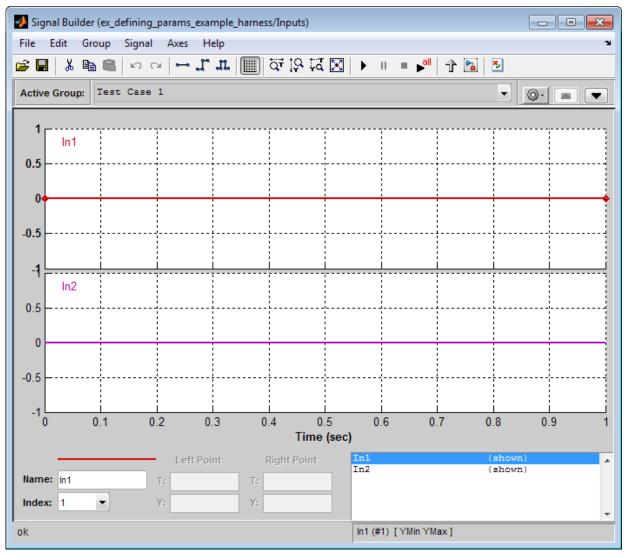

| Simulate Test Cases                                    | 5-19                                                      |

| Store Parameter Constraints in MATLAB Code Files       | 5-24                                                      |

| Export Parameter Constraints to File                   | 5-24                                                      |

| Import Parameter Constraints from File                 | 5-26                                                      |

| Define Constraint Values for Parameters in MATLAB Code | F 0=                                                      |

| Files                                                  | $\begin{array}{c} 5\text{-}27 \\ 5\text{-}27 \end{array}$ |

| Syntax in Parameter Configuration Files                | 5-27                                                      |

| •                                                      | •                                                         |

| и | ы | ď |

|---|---|---|

|   | , |   |

| и |   |   |

| • |   | _ |

|   |   |   |

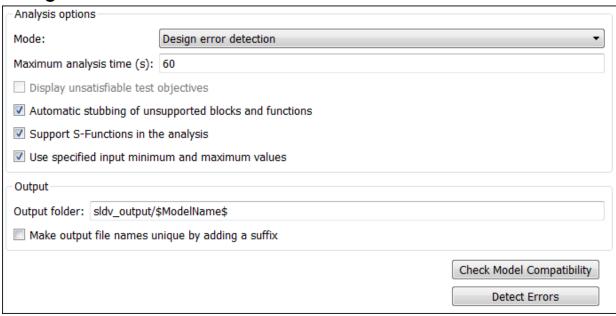

| What Is Design Error Detection?                 | 6-2          |

|-------------------------------------------------|--------------|

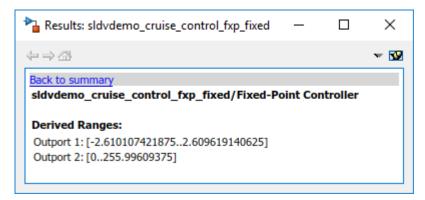

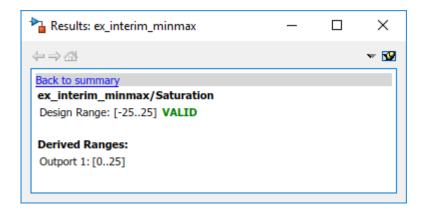

| Derived Ranges in Design Error Detection        | 6-3          |

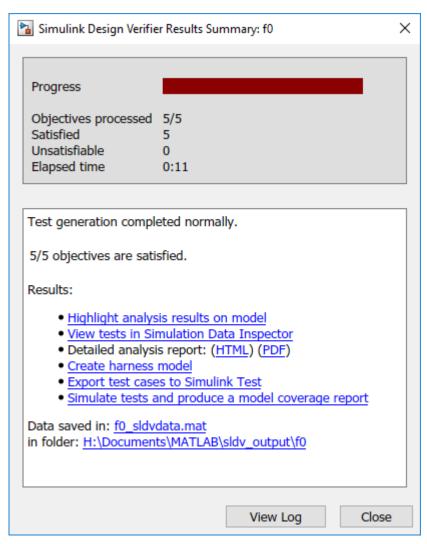

| Run a Design Error Detection Analysis           | 6-4<br>6-4   |

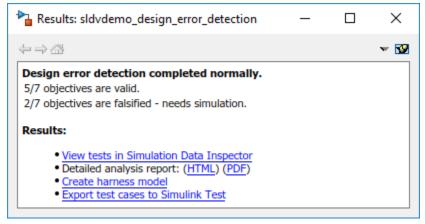

| Understand the Analysis Results                 | 6-4<br>6-7   |

| Check For Design Errors using the Model Advisor | 6-7          |

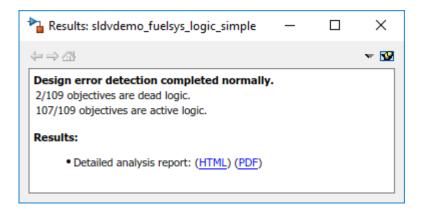

| Check a Model for Dead Logic                    | 6-9          |

| Analyze Models for Dead Logic                   | 6-9          |

| Common Causes of Dead Logic                     | 6-9          |

| Dead Logic Analysis Results                     | 6-9          |

| Dead Logic Detection                            | 6-10         |

| Detect Dead Logic Only                          | 6-10         |

| Detect Dead and Active Logic                    | 6-11         |

| Detect Dead Logic Caused by an Incorrect Value  | 6-12         |

| Analyze the Fuel System Model                   | 6-12         |

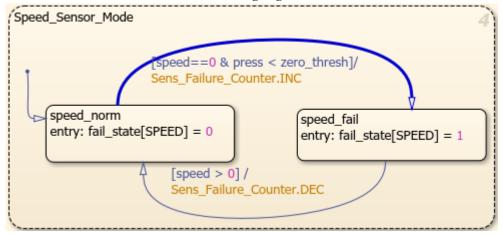

| Review the Results and Trace to the Model       | 6-13         |

| Investigate the Cause of the Dead Logic         | 6-14<br>6-14 |

| Model Objects That Receive Dead Logic Detection | 6-15         |

| Abs                                             | 6-16         |

| Dead Zone                                       | 6-16         |

| Discrete-Time Integrator                        | 6-17         |

| Enabled Subsystem                               | 6-17         |

| Enabled and Triggered Subsystem                 | 6-18         |

| Fcn                                             | 6-18         |

| For Iterator, For Iterator Subsystem            | 6-18         |

| If, If Action Subsystem                         | 6-19         |

| Library-Linked Objects                          | 6-19         |

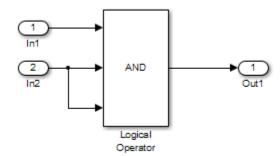

| Logical Operator                                | 6-19         |

| MATLAB Function                                 | 6-19<br>6-20 |

| MinMax                                          | 6-20         |

| INDUCT                                          | 0-40         |

| Multiport Switch                                                   |                         | 20        |

|--------------------------------------------------------------------|-------------------------|-----------|

| Rate Limiter                                                       |                         | 20        |

| Relay                                                              |                         | 21        |

| Saturation                                                         |                         | 21        |

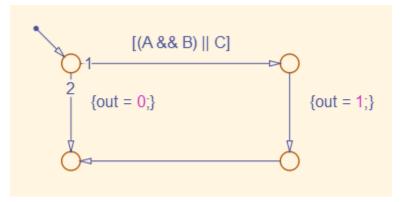

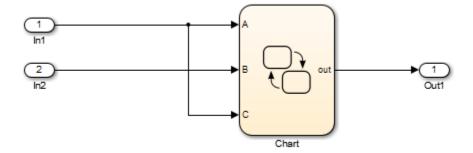

| Stateflow Charts                                                   | 6-                      | <b>22</b> |

| Switch                                                             |                         | <b>22</b> |

| SwitchCase, SwitchCase Action S                                    |                         | <b>22</b> |

| Triggered Models                                                   | 6-                      | <b>22</b> |

| Triggered Subsystem                                                |                         | <b>23</b> |

| While Iterator, While Iterator Su                                  | bsystem 6-              | 23        |

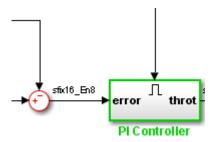

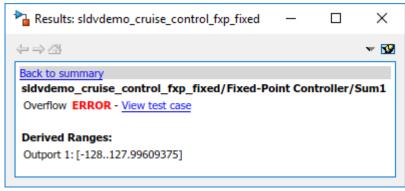

| Detect Integer Overflow and Divis                                  | sion-by-Zero Errors 6-  | 24        |

| About This Example                                                 |                         | 24        |

| Analyze the Model                                                  | 6-                      | 24        |

| Review the Analysis Results                                        | 6-                      | <b>25</b> |

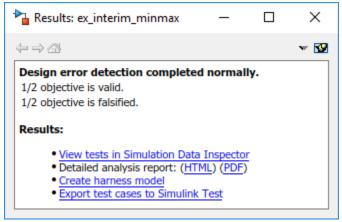

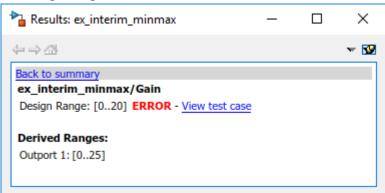

| Check for Specified Intermediate                                   | Minimum and Maximum     |           |

| Signal Values                                                      | 6-                      | 29        |

| Overview of Specified Minimum a                                    | and Maximum Signal      |           |

| Values                                                             | 6-                      | 29        |

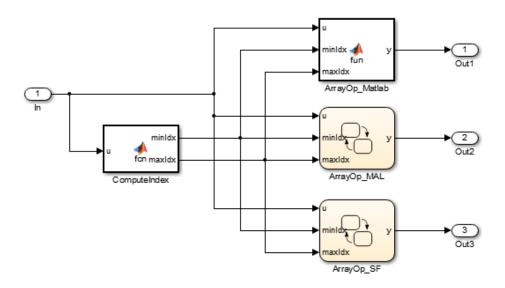

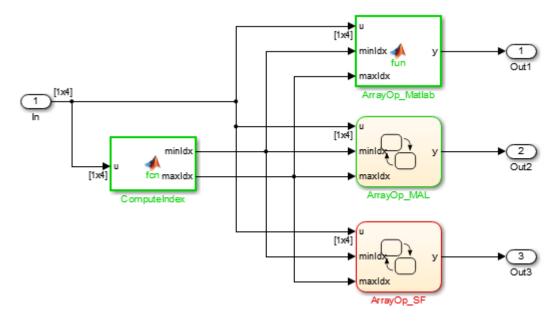

| About This Example                                                 | 6-                      | 30        |

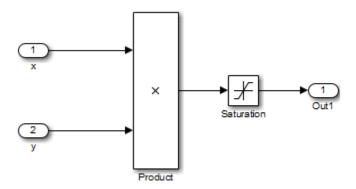

| Create the Example Model                                           |                         | 30        |

| Analyze the Model                                                  |                         | 32        |

| Review the Analysis Results                                        | 6-                      | 32        |

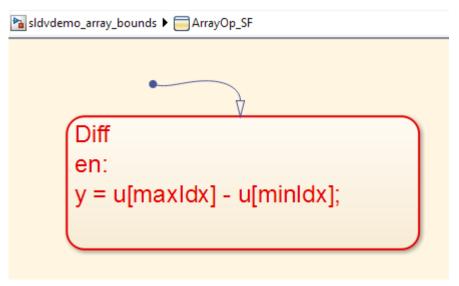

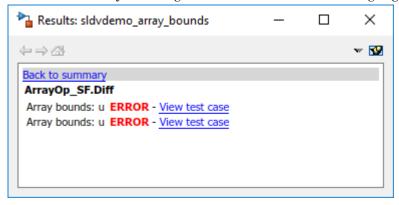

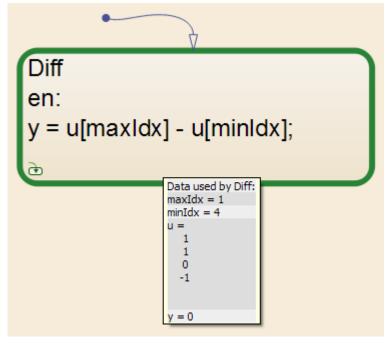

| Detect Out of Bound Array Access                                   | Errors 6-               | 36        |

| Design Error Detection for Out of                                  | f Bound Array Access 6- | 36        |

| Detect Out of Bound Array Access Limitations of Support for Out of |                         | 37        |

| Error Detection                                                    | ·                       | 42        |

| Error Beleevion                                                    | •                       |           |

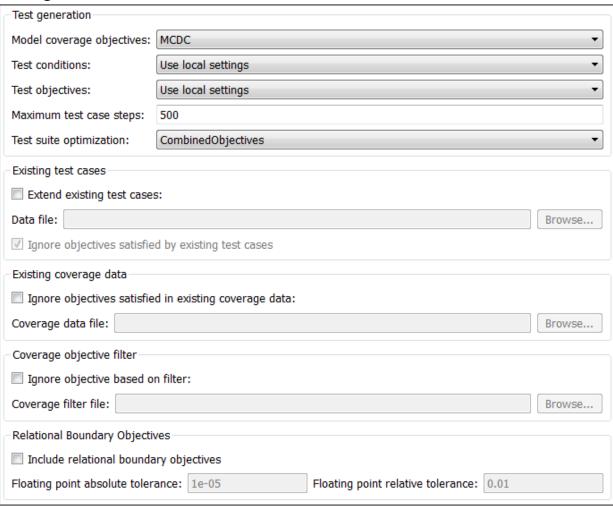

|                                                                    | Generating Test Case    | es        |

|                                                                    |                         |           |

| What Is Test Case Generation?                                      |                         | 7-2       |

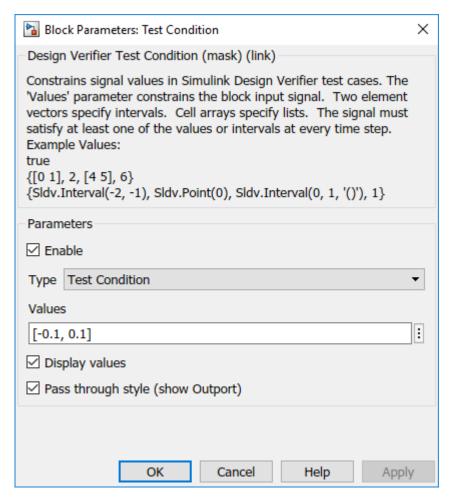

| Test Case Blocks                                                   |                         | 7-2       |

| Test Case Functions                                                |                         | 7-2       |

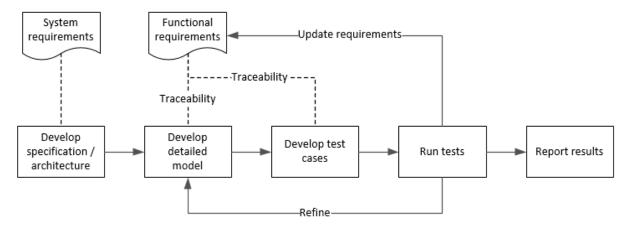

| Workflow for Test Case Generation                                  | n                       | 7-4       |

|                                                                    |                         |           |

|            | Generate Test Cases for Model Decision Coverage                                                                                                         | 7-5                              |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

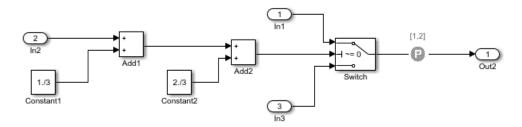

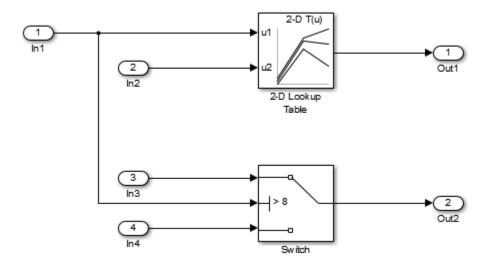

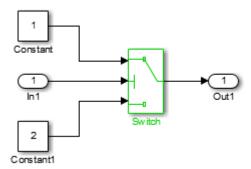

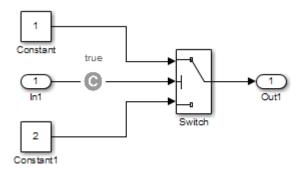

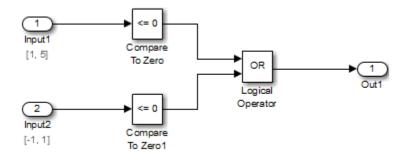

|            | Construct the Example Model                                                                                                                             | 7-5                              |

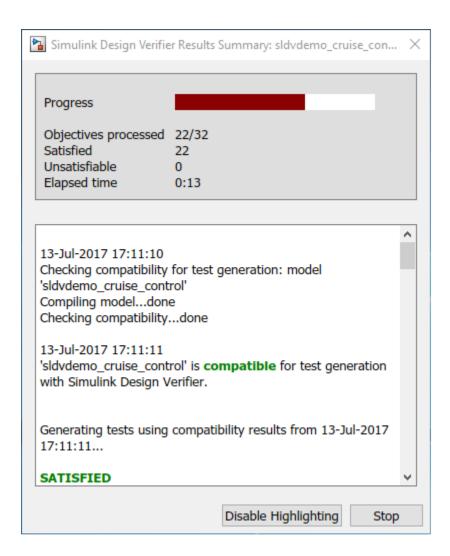

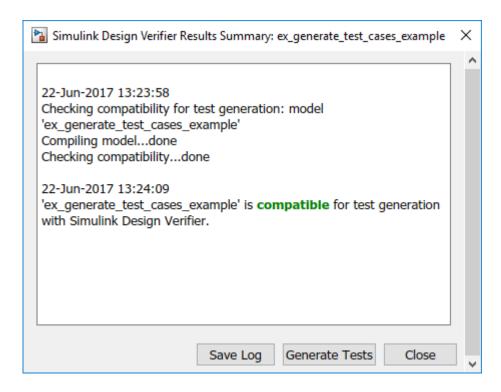

|            | Check Compatibility of the Example Model                                                                                                                | 7-6                              |

|            | Configure Test Generation Options                                                                                                                       | 7-7                              |

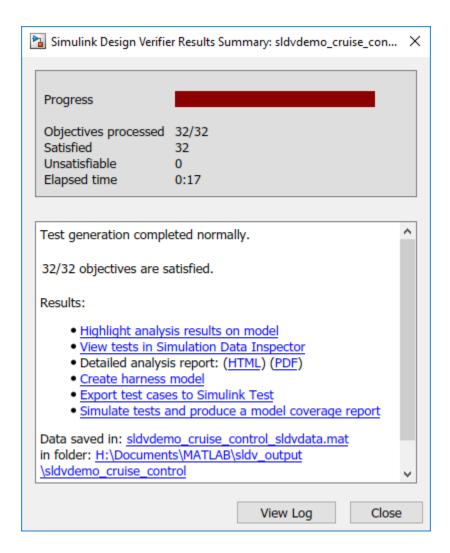

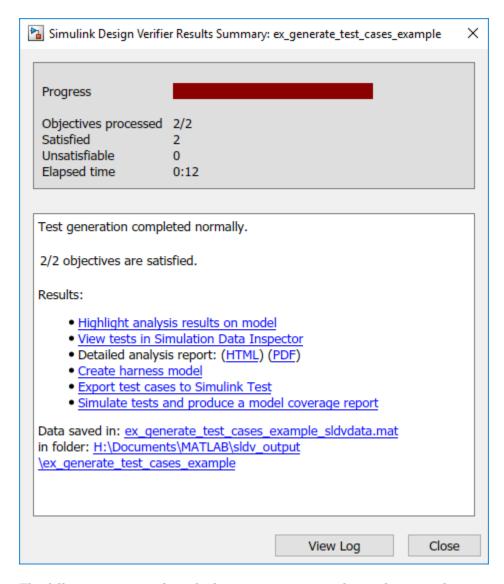

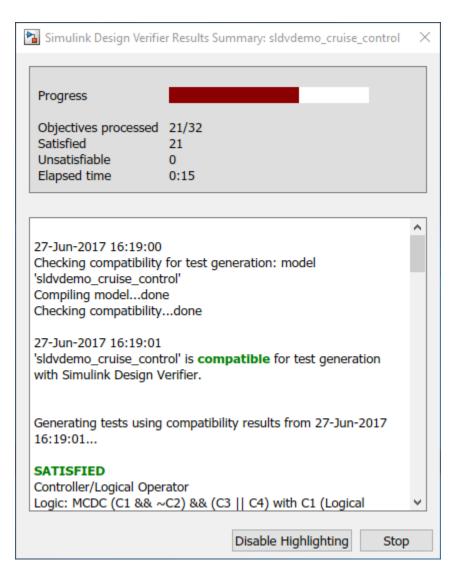

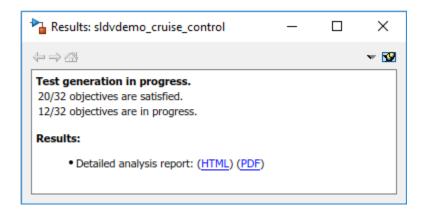

|            | Analyze the Example Model                                                                                                                               | <b>7</b> -8                      |

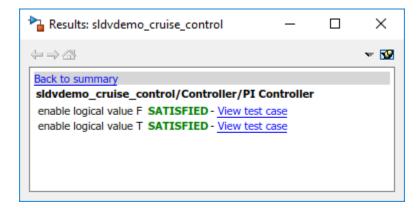

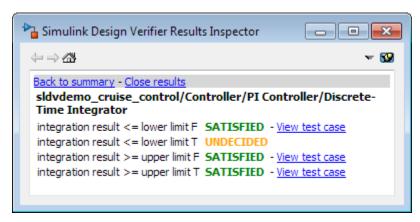

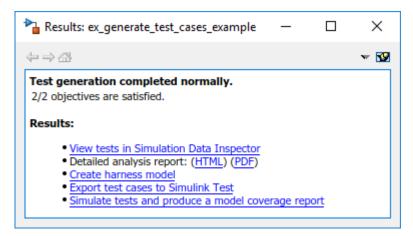

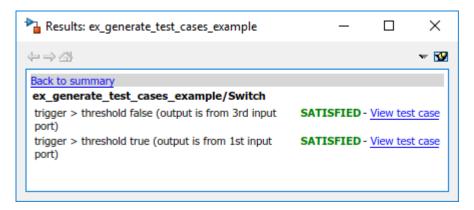

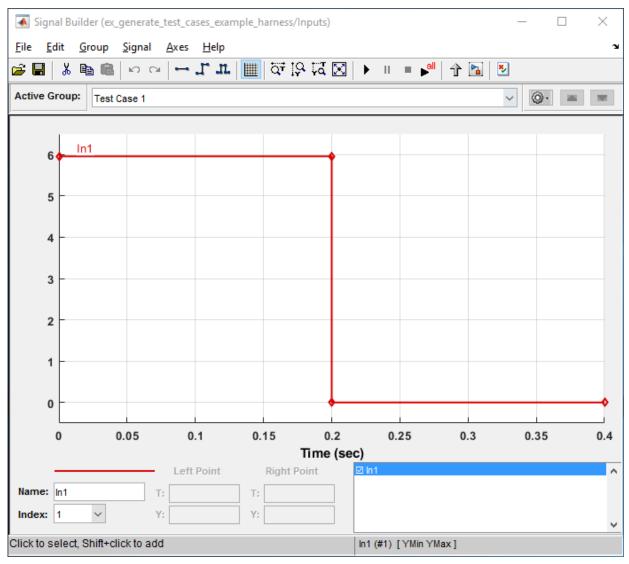

|            | Review Analysis Results                                                                                                                                 | <b>7-8</b>                       |

|            | Customize Test Generation                                                                                                                               | 7-17                             |

|            | Reanalyze the Example Model                                                                                                                             | <b>7-19</b>                      |

|            | Analyze Contradictory Models                                                                                                                            | 7-21                             |

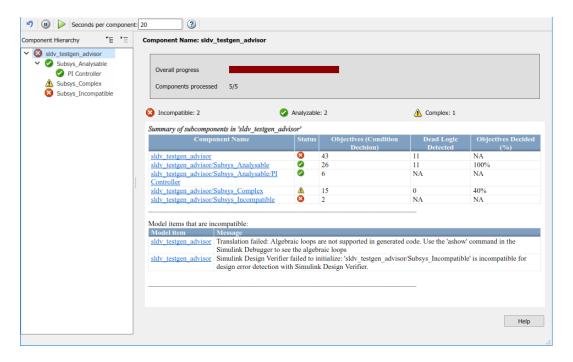

|            | Use Test Generation Advisor to Identify Analyzable                                                                                                      |                                  |

|            | Components                                                                                                                                              | 7-22                             |

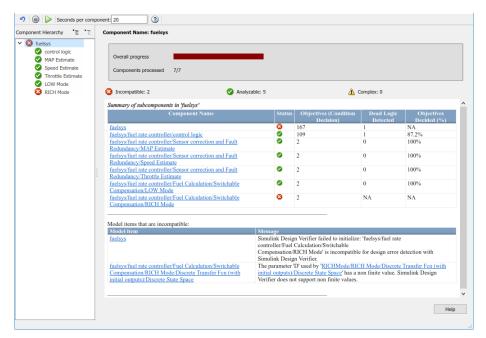

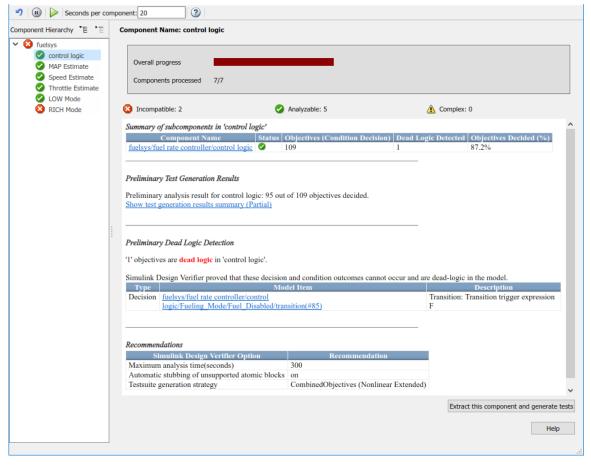

|            | Test Generation Advisor                                                                                                                                 | 7-22                             |

|            | Test Generation Advisor Requirements                                                                                                                    | <b>7-24</b>                      |

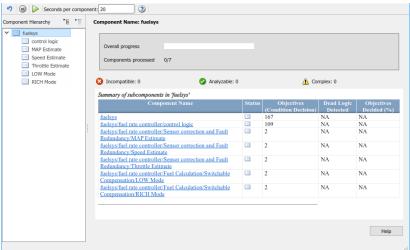

|            | Identify Analyzable Components                                                                                                                          | <b>7-24</b>                      |

|            | Analyze and Generate Tests for Model Components                                                                                                         | <b>7-24</b>                      |

|            | Manually Select Components for Testing                                                                                                                  | 7-27                             |

|            | Model Coverage Objectives for Test Generation                                                                                                           | 7-29                             |

|            | Decision                                                                                                                                                | 7-29                             |

|            | Condition                                                                                                                                               | 7-29                             |

|            | MCDC                                                                                                                                                    | 7-30                             |

|            | Relational Boundary                                                                                                                                     | 7-30                             |

| <b>0</b> [ | Extending Existing Test Ca                                                                                                                              | ases                             |

| 8          |                                                                                                                                                         |                                  |

|            | When to Extend Existing Test Cases                                                                                                                      | 8-2                              |

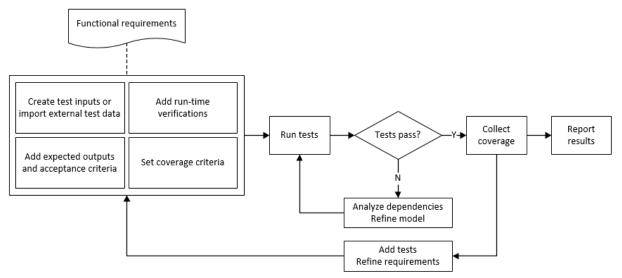

|            | Common Workflow for Extending Existing Test Cases                                                                                                       | 8-4                              |

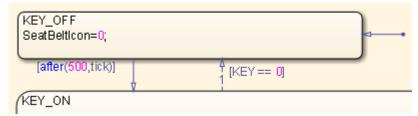

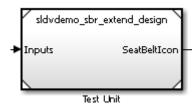

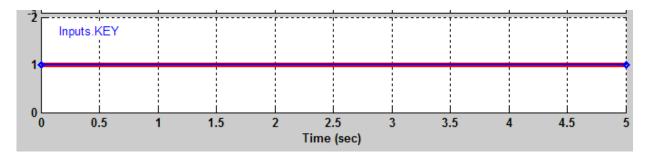

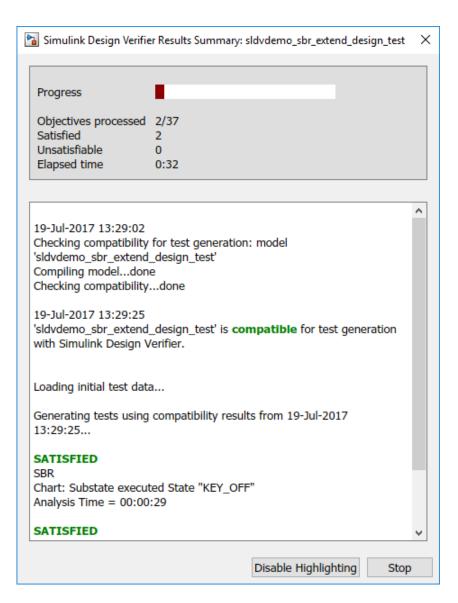

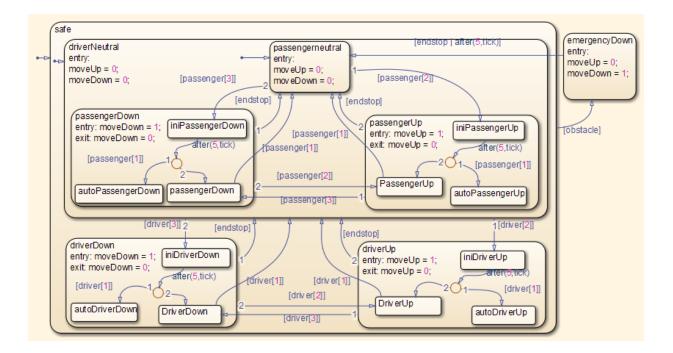

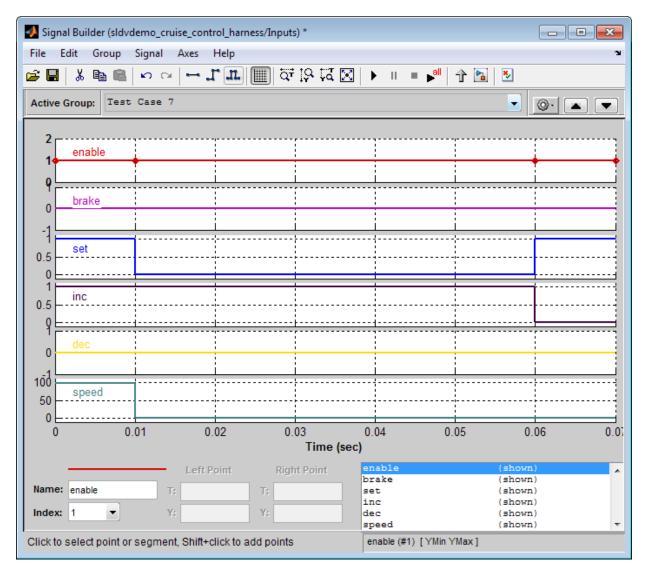

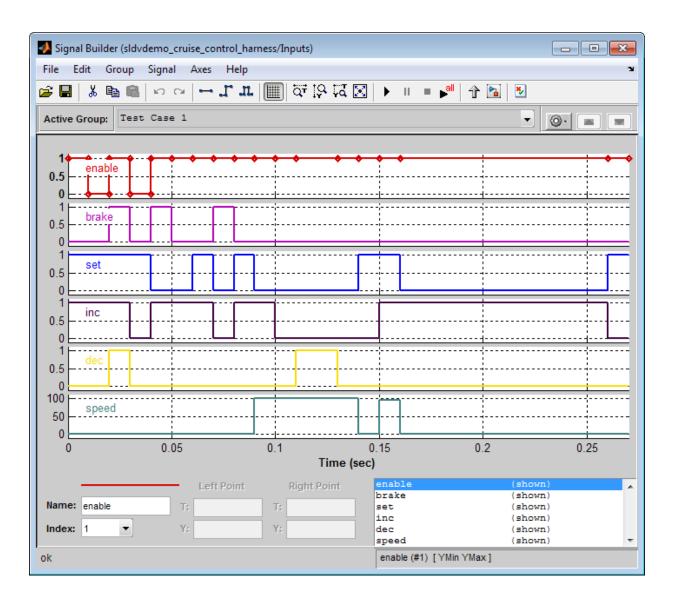

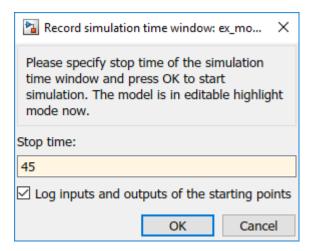

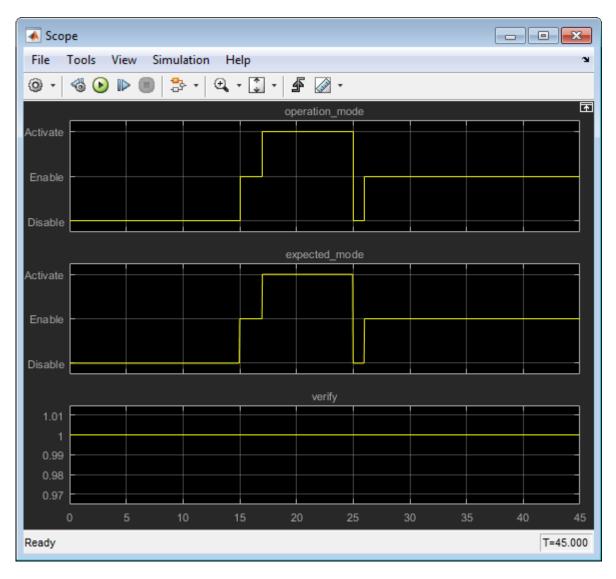

|            | Extend Test Cases for Model with Temporal Logic  Create Starting Test Case  Log Starting Test Case  Extend Existing Test Cases  Verify Analysis Results | 8-5<br>8-5<br>8-8<br>8-9<br>8-11 |

|            | Extend Test Cases for Closed-Loop System                                                                                                                | 8-12<br>8-12<br>8-15             |

|   | Extend Test Cases for Modified Model                                                                                                | 8-19<br>8-19<br>8-20 |

|---|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 9 | Achieving Test Cases for Missing Model Cover                                                                                        | age                  |

| · | Generate Test Cases for Missing Coverage Data                                                                                       | 9-2                  |

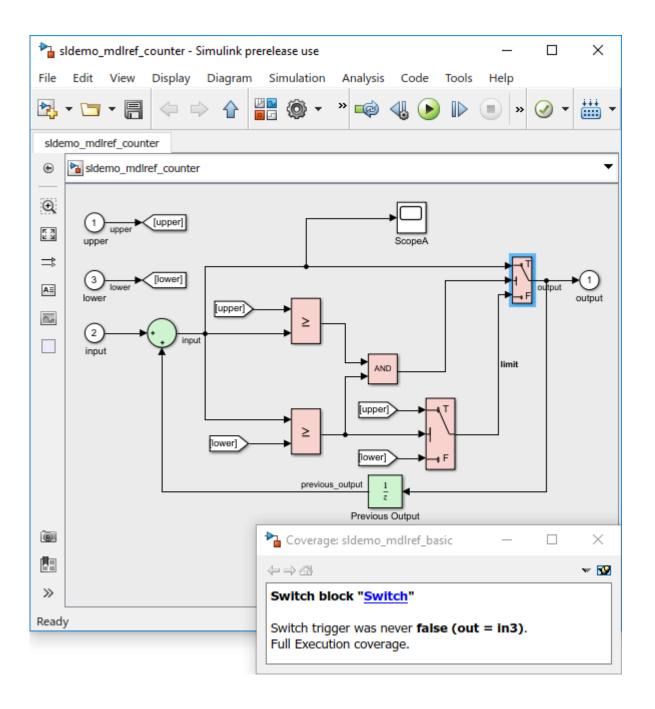

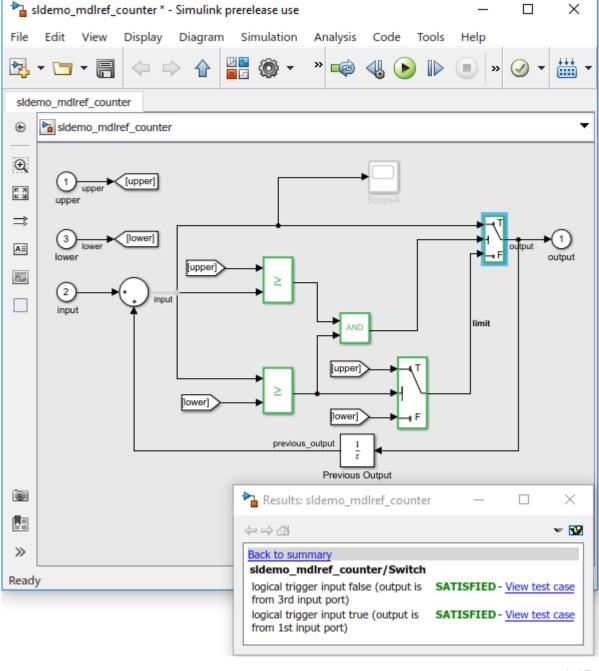

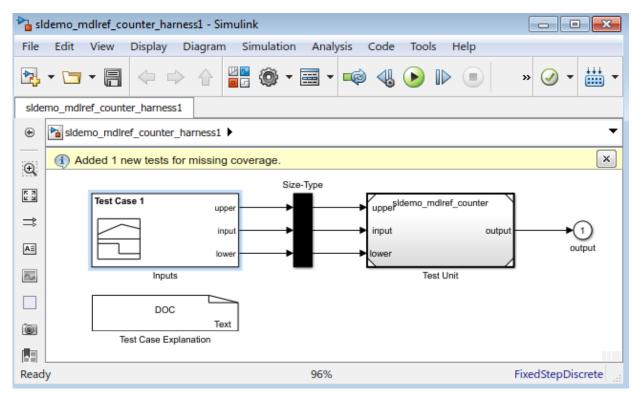

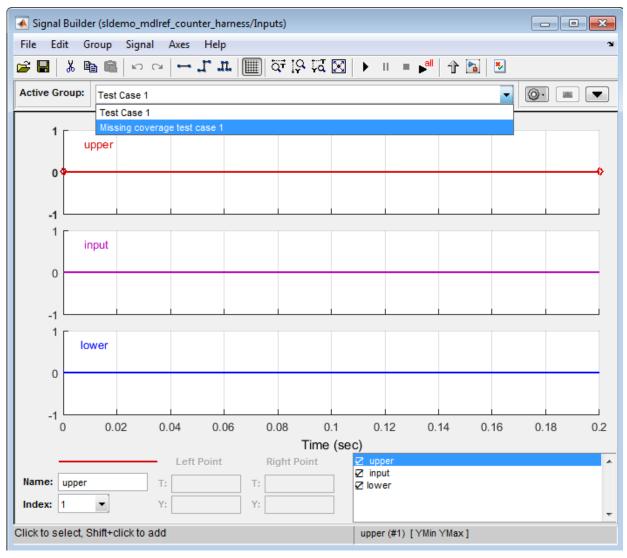

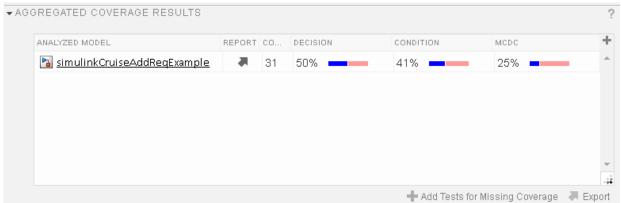

|   | Achieve Missing Coverage in Referenced Model Programmatically Achieve Missing Coverage in Referenced                                | 9-3                  |

|   | Model                                                                                                                               | 9-3                  |

|   | Harness  Missing Coverage in Subsystems and Model Blocks                                                                            | 9-6<br>9-12          |

|   | Achieve Missing Coverage in Closed-Loop Simulation  Model  Record Coverage Data for the Model  Find Test Cases for Missing Coverage | 9-13<br>9-13<br>9-14 |

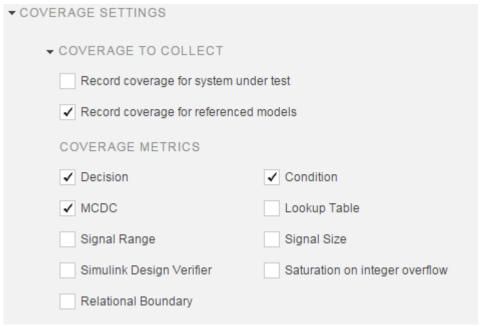

|   | Modified Condition and Decision Coverage in Simulink  Design Verifier                                                               | 9-16<br>9-16         |

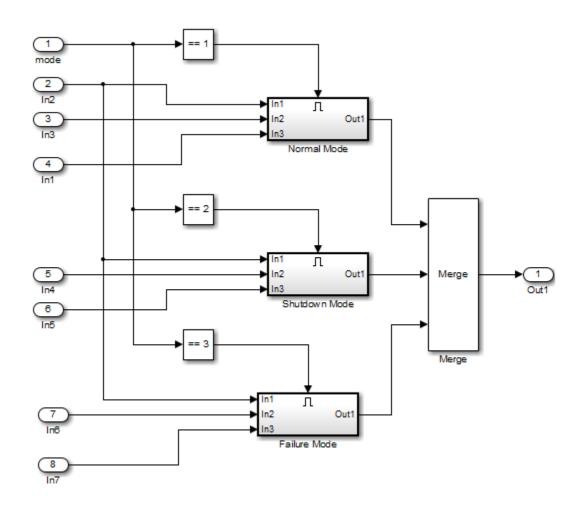

| 0 | Verifying Model Compone                                                                                                             | ents                 |

|   | What Is Component Verification?                                                                                                     | 10-2<br>10-2         |

|   | Verification                                                                                                                        | 10-2<br>10-4         |

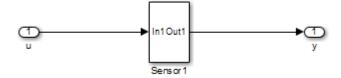

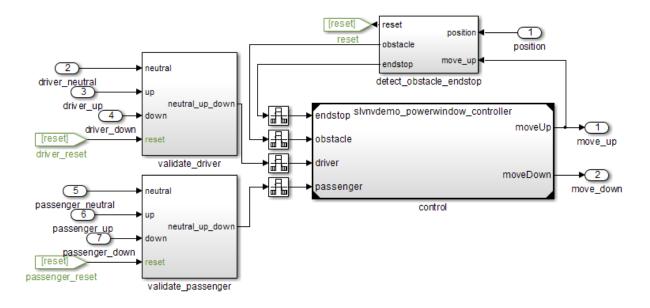

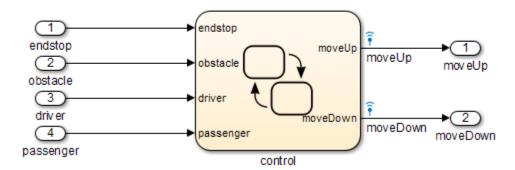

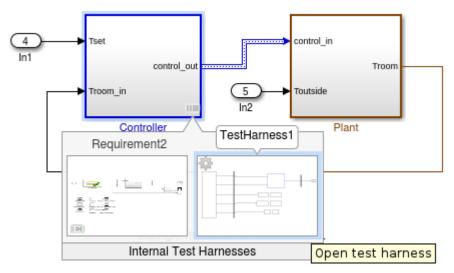

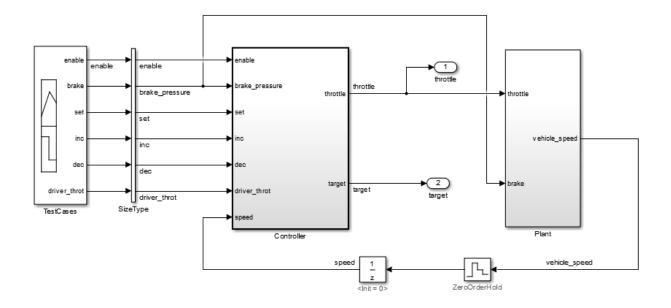

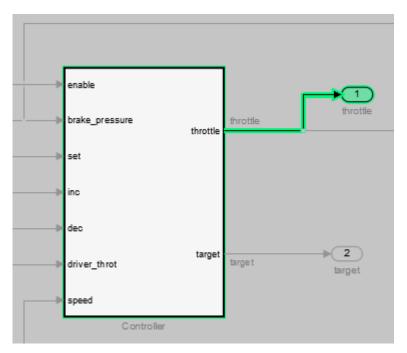

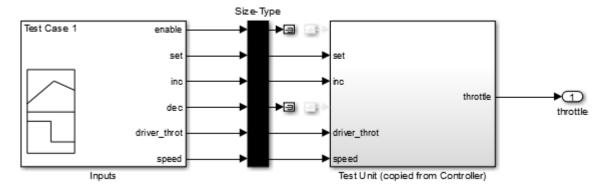

|             | About the Example Model Prepare the Component for Verification Record Coverage for the Component Use Simulink Design Verifier Software to Record Additional Coverage Combine the Harness Models Execute the Component in Simulation Mode Execute the Component in Software-in-the-Loop (SIL) Mode | 10-6<br>10-8<br>10-10<br>10-12<br>10-13<br>10-13 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| <b>11</b> [ | Considering Specified Minimum and Maxim<br>Values for Inputs During Ana                                                                                                                                                                                                                           |                                                  |

| 1           | Minimum and Maximum Input Constraints                                                                                                                                                                                                                                                             | 11-2                                             |

|             | Simulink Design Verifier Support for Specified Input Minimum and Maximum Values                                                                                                                                                                                                                   | n<br>11-2                                        |

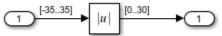

|             | Minimum and Maximum Values                                                                                                                                                                                                                                                                        | 11-3                                             |

|             | Specify Input Ranges on Simulink and Stateflow                                                                                                                                                                                                                                                    | 11 /                                             |

|             | Elements                                                                                                                                                                                                                                                                                          | 11-4<br>11-4                                     |

|             | Specify Input Ranges for Simulink.Signal Objects                                                                                                                                                                                                                                                  | 11-4                                             |

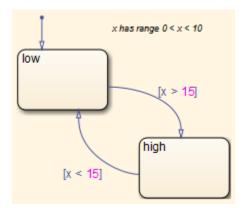

|             | Specify Input Ranges for Stateflow Data Objects                                                                                                                                                                                                                                                   | 11-6                                             |

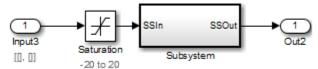

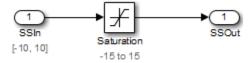

|             | Specify Input Ranges for Subsystems                                                                                                                                                                                                                                                               | 11-7                                             |

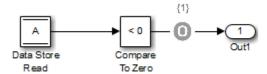

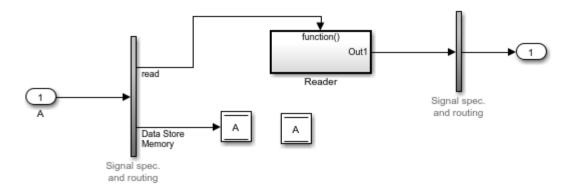

|             | Specify Input Ranges for Global Data Stores                                                                                                                                                                                                                                                       | 11-8                                             |

|             | Specify Input Ranges for Bus Elements                                                                                                                                                                                                                                                             | 11-9                                             |

|             | Specify Input Ranges in sldvData Fields                                                                                                                                                                                                                                                           | 11-11                                            |

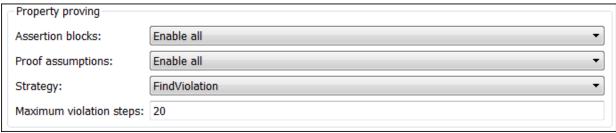

| 10          | Proving Properties of a M                                                                                                                                                                                                                                                                         | lodel                                            |

| 12          |                                                                                                                                                                                                                                                                                                   |                                                  |

|             | What Is Property Proving?                                                                                                                                                                                                                                                                         | 12-2 $12-2$                                      |

|             | 1 1001 DI0029                                                                                                                                                                                                                                                                                     | 14-4                                             |

|   | Proof Functions                                       | 12-2         |

|---|-------------------------------------------------------|--------------|

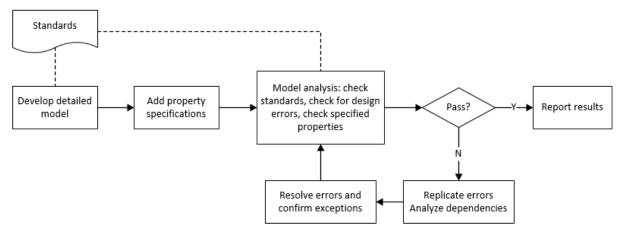

|   | Workflow for Proving Model Properties                 | 12-4         |

|   | Prove Properties in a Model                           | 12-5         |

|   | About This Example                                    | 12-5         |

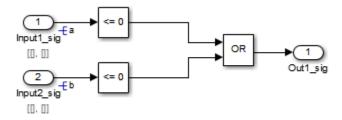

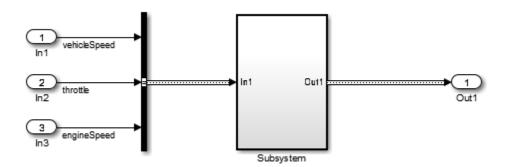

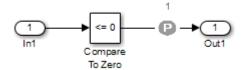

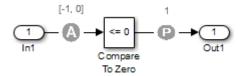

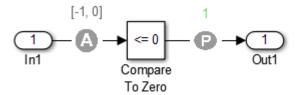

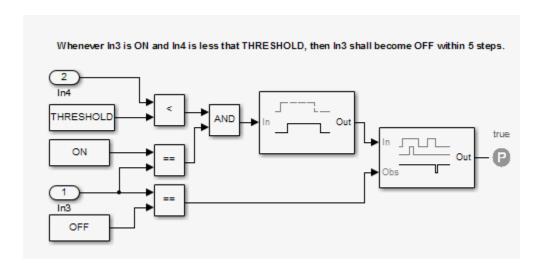

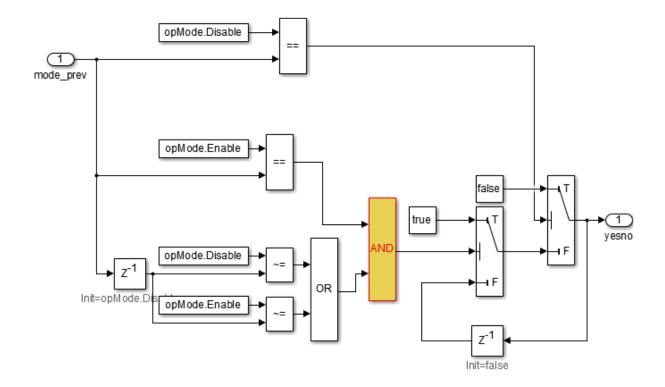

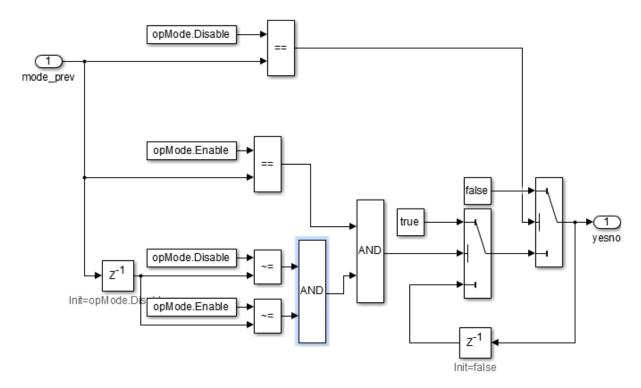

|   | Construct Example Model                               | 12-6         |

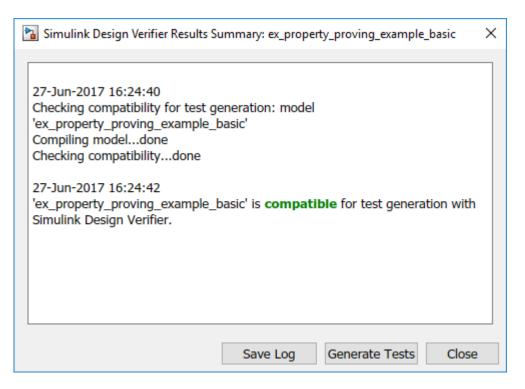

|   | Check Compatibility of Example Model                  | 12-7         |

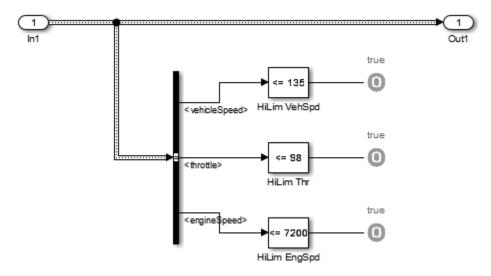

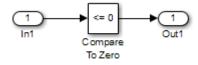

|   | Instrument Example Model                              | 12-8         |

|   | Configure Property-Proving Options                    | 12-9         |

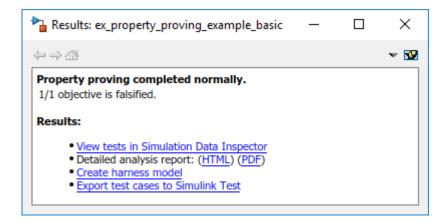

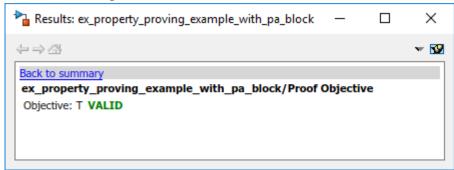

|   | Analyze Example Model                                 | 12-10        |

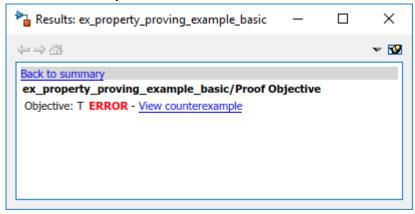

|   | Review Analysis Results                               | 12-10        |

|   | Customize Example Proof                               | 12-19        |

|   | Reanalyze Example Model                               | 12-20        |

|   | Review Results of Second Analysis                     | 12-20        |

|   | Analyze Contradictory Models                          | 12-23        |

|   | Prove Properties in a Large Model                     | 12-24        |

|   | Prove System-Level Properties Using Verification      |              |

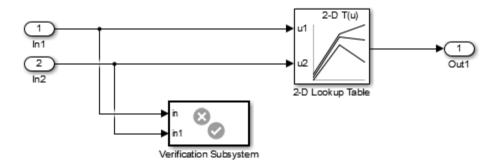

|   | Model                                                 | 12 - 25      |

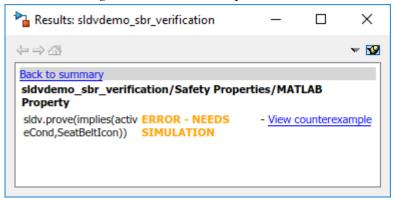

|   | When to Use a Verification Model for Property Proving | 12 - 25      |

|   | About this Example                                    | 12 - 25      |

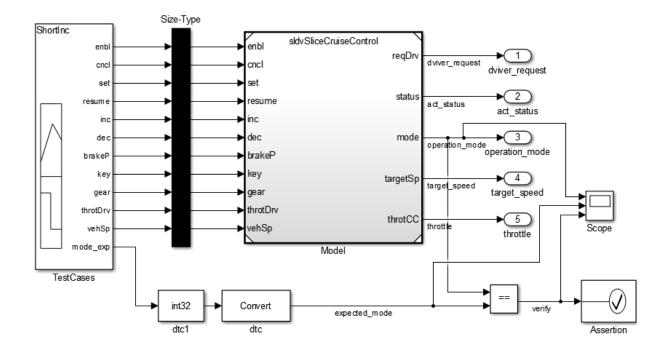

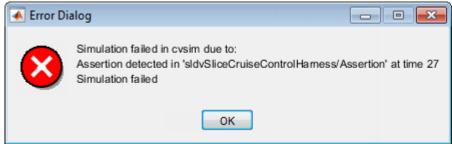

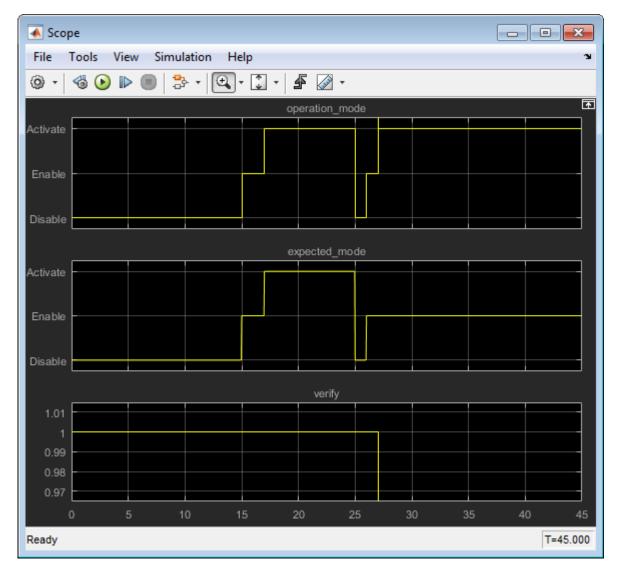

|   | Understand the Verification Model                     | 12 - 25      |

|   | Prove the Properties of the Design Model              | 12-26        |

|   | Fix the Verification Model                            | <b>12-27</b> |

|   | Prove Properties in a Subsystem                       | 12-29        |

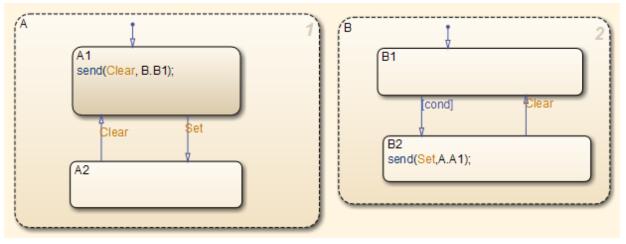

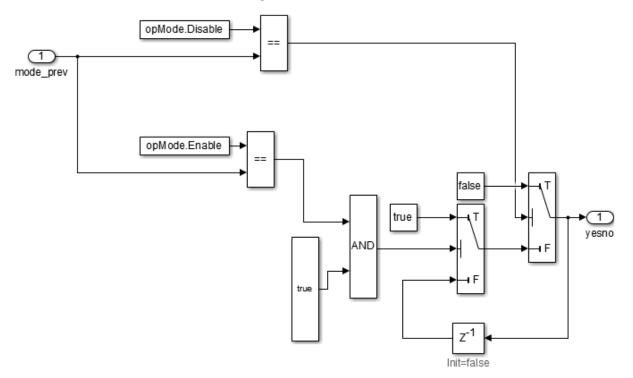

|   | Model Requirements                                    | 12-30        |

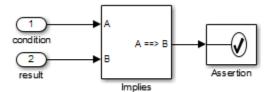

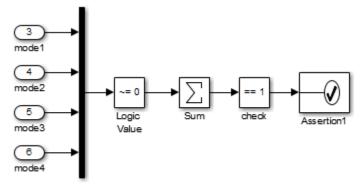

|   | Basic Properties                                      | 12-30        |

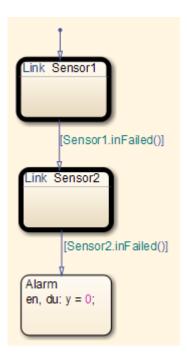

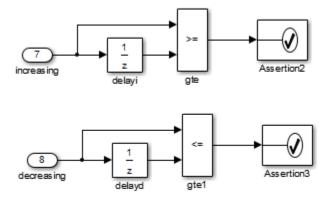

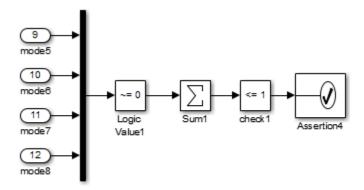

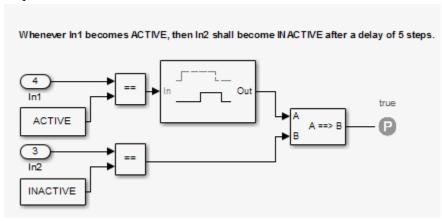

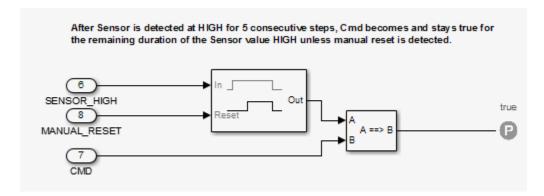

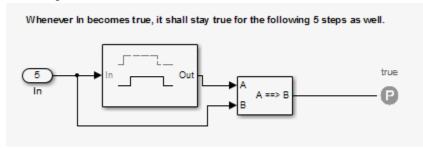

|   | Temporal Properties                                   | 12-32        |

|   |                                                       |              |

|   | Reviewing the Re                                      | sults        |

| 3 |                                                       |              |

|   | Highlighted Results on the Model                      | 13-2         |

|   | Results Review with Model Highlighting                | 13-2         |

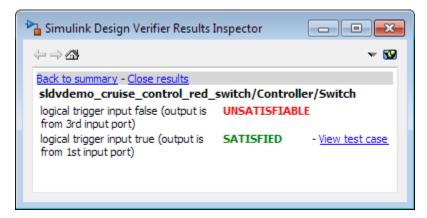

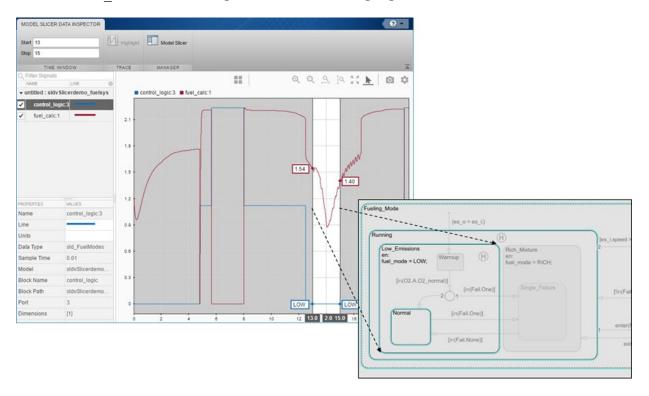

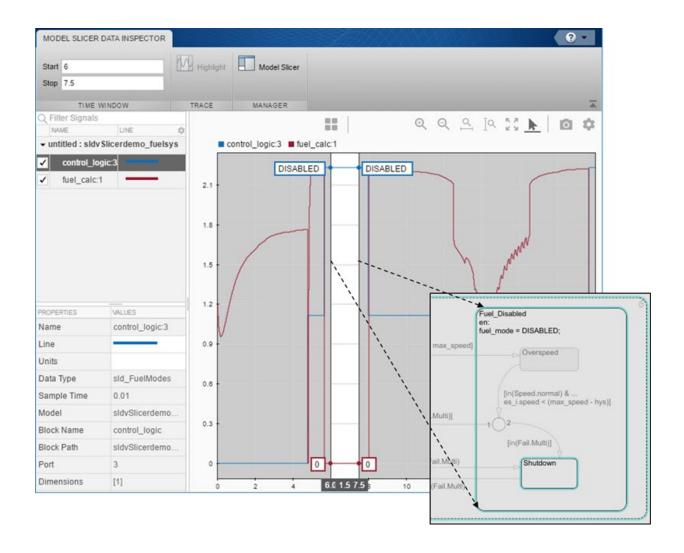

|   | Simulink Design Verifier Results Inspector            | 13-2         |

|   | Highlight Results on Model Automatically              | 13-2         |

|   | Green Highlighting on Model                           | 13-4         |

|   |                                                       |              |

| Red Highlighting on Model                  | 13-5  |

|--------------------------------------------|-------|

| Orange Highlighting on Model               | 13-5  |

| Gray Highlighting on Model                 | 13-8  |

|                                            |       |

| Simulink Design Verifier Data Files        | 13-9  |

| Data File Generation                       | 13-9  |

| Contents of sldvData Structure             | 13-9  |

| Model Information Fields in sldvData       | 13-10 |

| Simulate Models with Data Files            | 13-15 |

| Load Results from Data Files               | 13-15 |

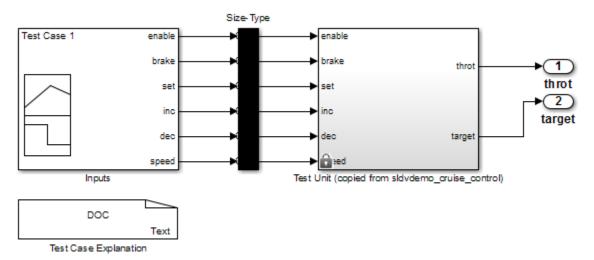

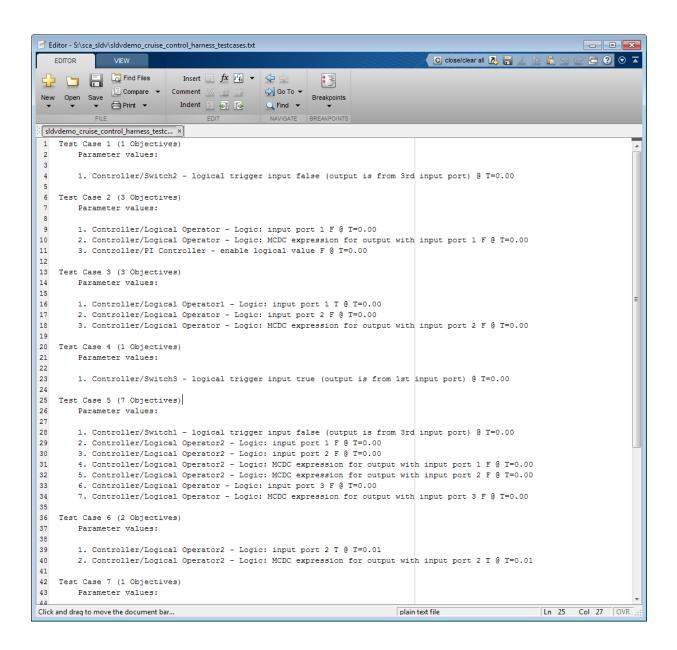

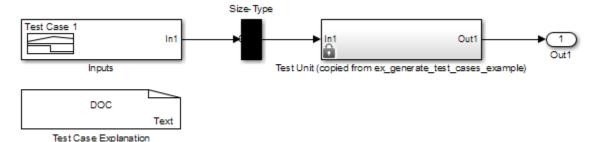

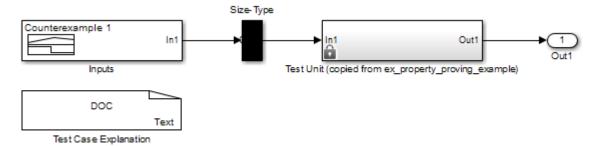

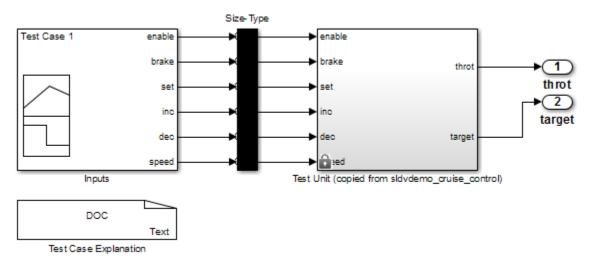

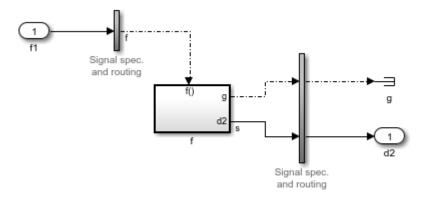

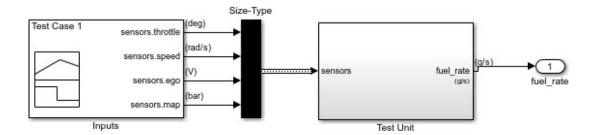

| Simulink Design Verifier Harness Models    | 13-16 |

| Harness Model Generation                   | 13-16 |

| Create a Harness Model                     | 13-16 |

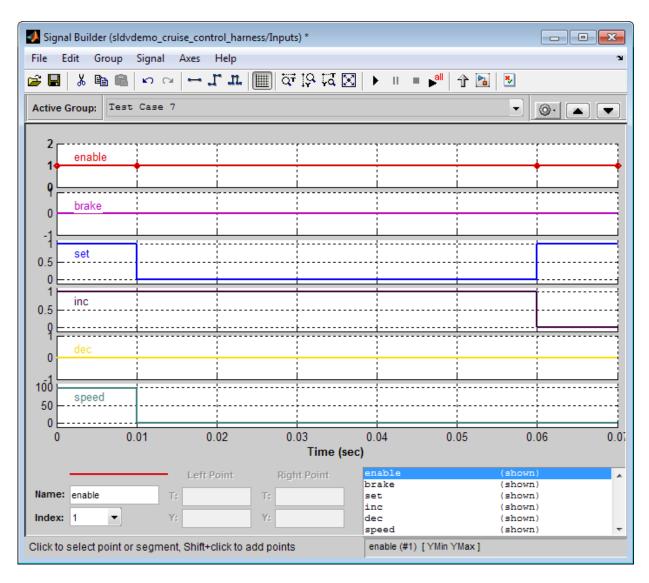

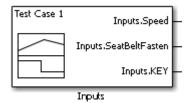

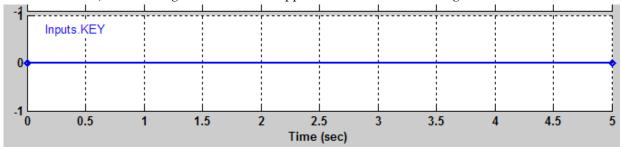

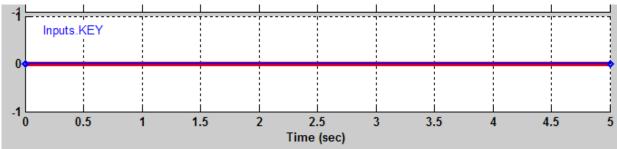

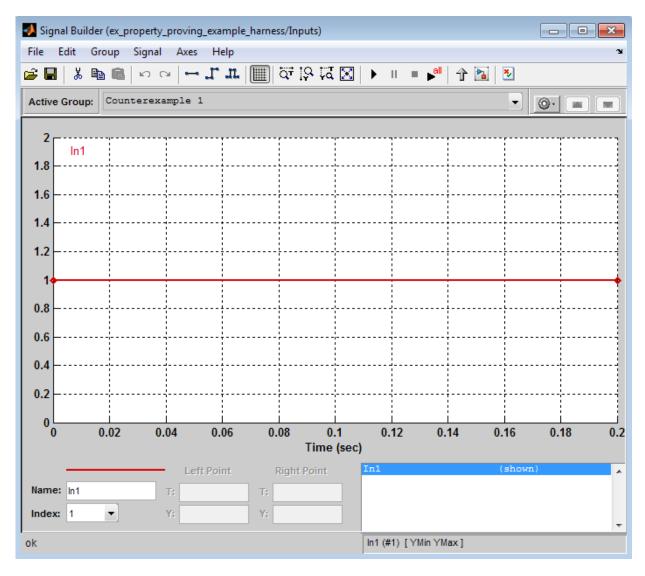

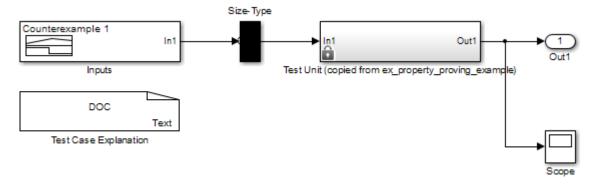

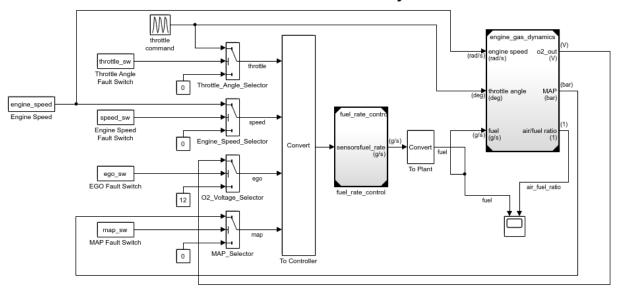

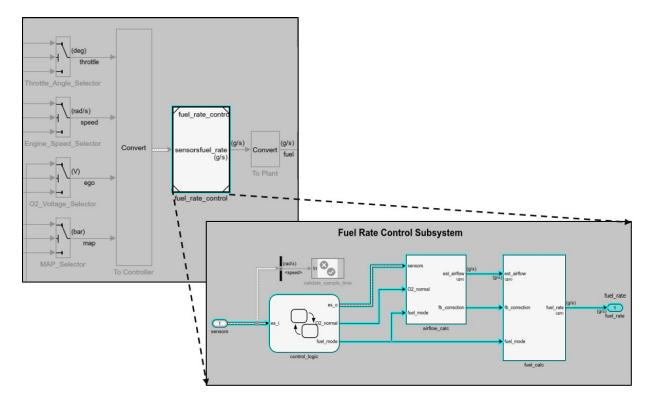

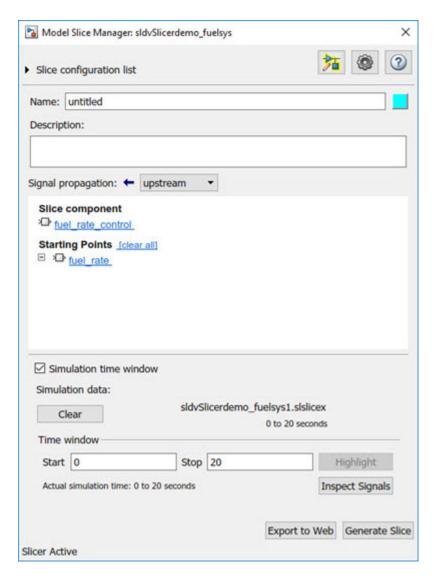

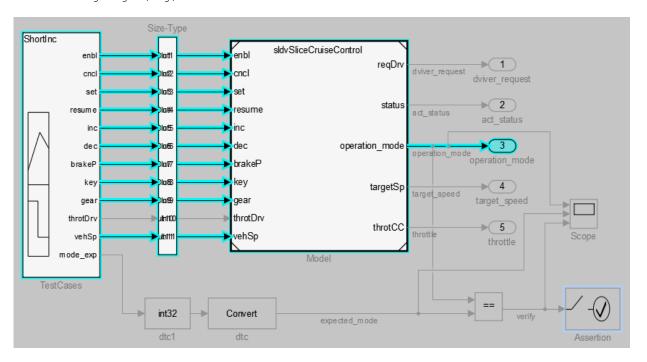

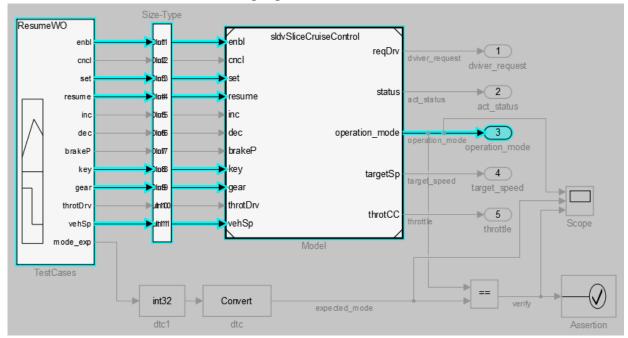

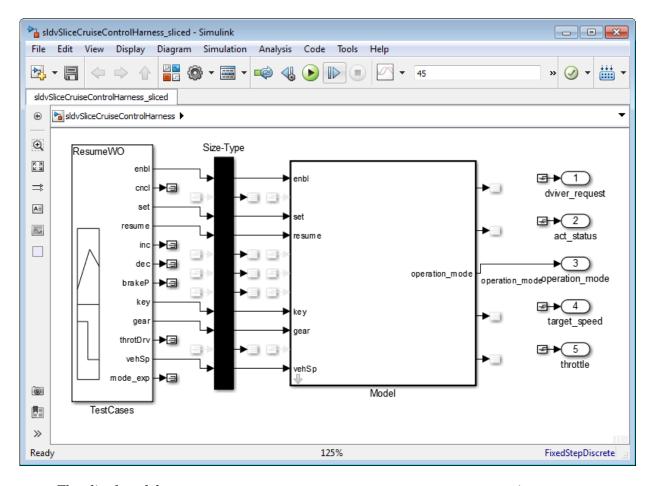

| Anatomy of a Harness Model                 | 13-17 |

| Configuration of the Harness Model         | 13-21 |

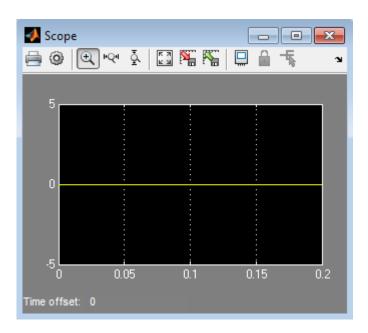

| Simulate the Harness Model                 | 13-22 |

|                                            | 10    |

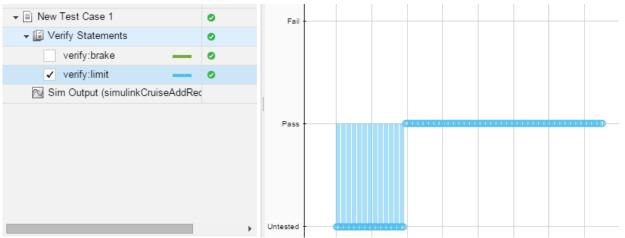

| Export Test Cases to Simulink Test         | 13-24 |

| Overall Workflow                           | 13-24 |

| Test Case Generation Example               | 13-24 |

| F                                          | -     |

| Simulink Design Verifier Reports           | 13-27 |

| Simulink Design Verifier Report Generation | 13-27 |

| Create Analysis Reports                    | 13-27 |

| Front Matter                               | 13-28 |

| Summary Chapter                            | 13-28 |

| Analysis Information Chapter               | 13-28 |

| Derived Ranges Chapter                     | 13-33 |

| Objectives Status Chapters                 | 13-34 |

| Model Items Chapter                        | 13-44 |

| Design Errors Chapter                      | 13-45 |

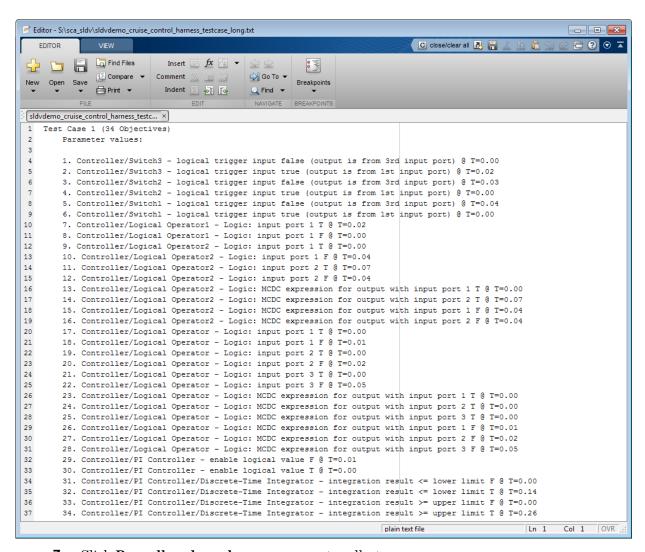

| Test Cases Chapter                         | 13-46 |

| Properties Chapter                         | 13-51 |

|                                            |       |

| Simulink Design Verifier Log Files         | 13-53 |

| Review Analysis Results                    | 13-55 |

| View Active Results                        | 13-55 |

| Load Previous Results                      | 13-55 |

| Explore Results                            | 13-56 |

| Emplore recognition                        | 10 00 |

## Analyzing Large Models and Improving Performance

| 1 | 4 |

|---|---|

|   |   |

| Sources of Model Complexity                                                                                                                                                                                                                | 14-2                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Analyze a Large Model  Types of Large Model Problems  Summarize Model Hierarchy and Compatibility  Use the Default Parameter Values  Modify the Analysis Parameters  Use the Large Model Optimization  Stop the Analysis Before Completion | 14-3<br>14-3<br>14-4<br>14-6<br>14-6      |

| Increase Allocated Memory for Analysis Report<br>Generation                                                                                                                                                                                | 14-8                                      |